关于PCIe :

PCIe是一种高速的序列式总线接口,它能够将电脑的主板和各种扩充卡连接在一起,实现数据的传输和通讯。自2001年开始,Intel在IDF(Intel Developer Forum)上公布了3GIO(Third Generation I/O)的概念后,来年正式定名为PCI Express,PCIe就正式走入PC界,成为了一种新的标准。

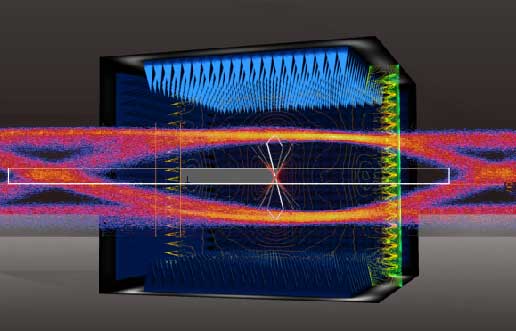

PCIe的高带宽设计,让它可以支持更多的应用和需求,从最初的Gen 1,每条线路传输速度仅2.5 GT/s(Giga Transfers per second),直至现在火红的Gen 5,每条线路传输速度高达32.0 GT/s,提升了12.8倍之多,这对在不同应用层,如:Storage(储存装置)、VGA(视频显示适配器)或是需要大数据传输进行运算的领域是相当受用的。然而在面对如此高速的PCIe Gen 5接口时,其验证方式肯定是比以往的Gen 3/ 4世代更加严苛,而这部分,就是许多厂商难以跨越的门槛。

验证内容与其导致的严重潜在风险

需验证PCIe Gen5的产品首先要面对的包含以下三大项:

- 搭配的治具板设计是否到位?

- 是否依照协会PCIe-SIG PCIe Gen 5 规范进行设计?

- 所设计出来的治具板是否能通过PCIe-SIG PCIe Gen 5 的测试标准?PCIe Gen 5规范在IL/RL/FEXT/NEXT这些S-Parameter上都有较之前Gen 3/ Gen 4严格的设定,为的就是避免用户在PCIe Gen 5的装置上使用时,有不愉快的体验而设下标准,而这就是Allion开发PCIe Gen 5 Socket CEM board的初衷-前期就能够协助客户解决产品验证的问题,进而提升产品的竞争力与市场占有率。

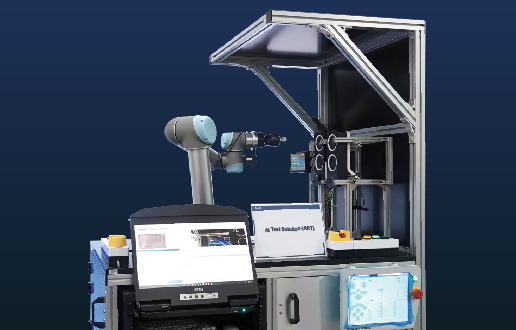

百佳泰提供完善的解决方案:

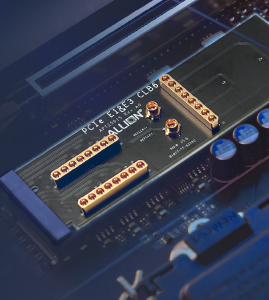

为了协助想开发PCIe Gen 5装置的厂商对协会规范作验证,Allion制作出PCIe 5.0 Socket的CEM board 来针对高频的讯号作验证,其特点是采用了SMPM连接器,除了方便及简化连接测试用的SMA Cable外,也提供除了现在Cable验证用的前4 lanes之外,剩余12 条Lanes的测试环境,这对现在或未来有完整16条lanes测试需求的厂商来说是相当受用的。

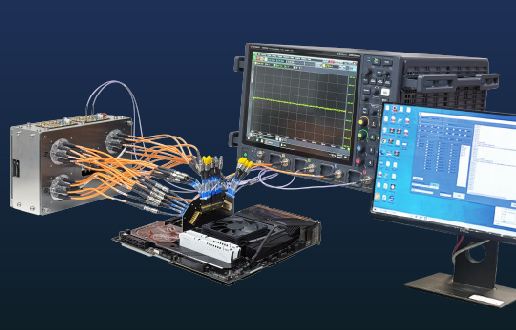

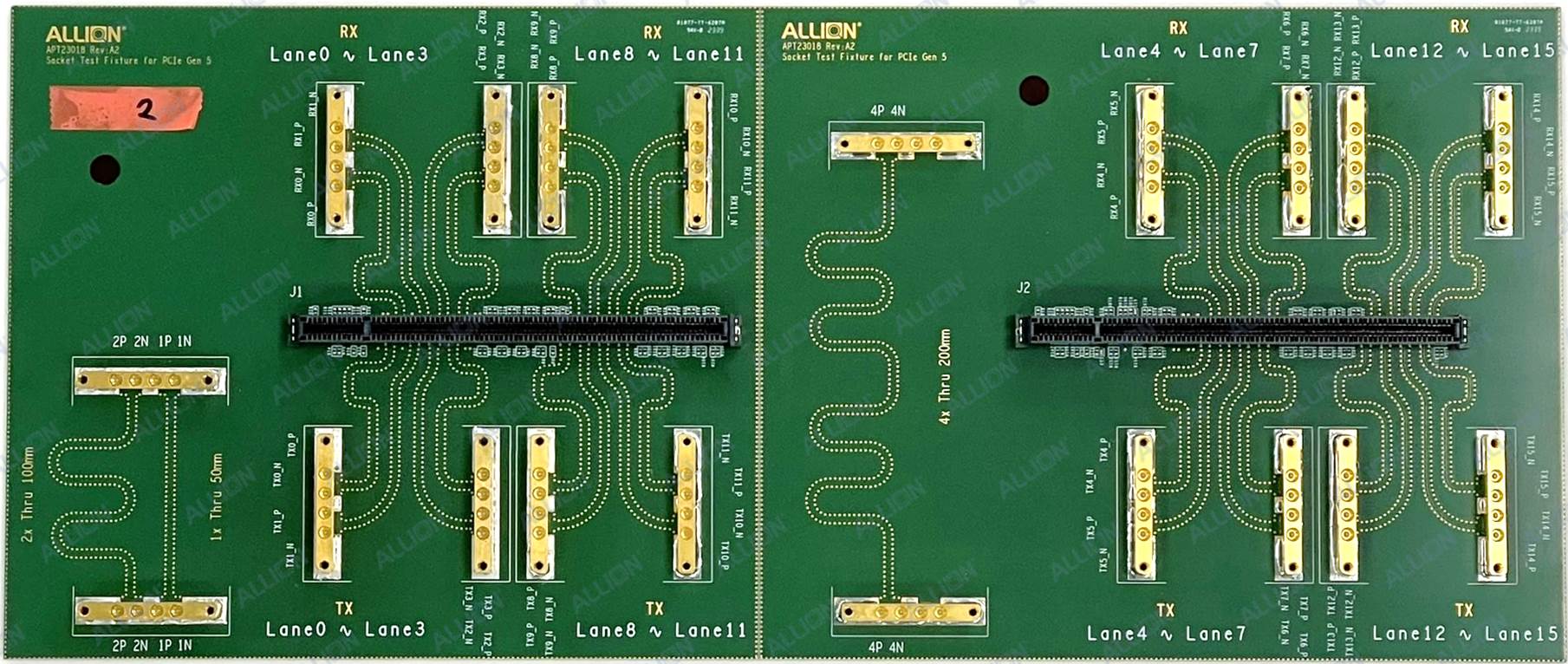

下图为Allion PCIe 5.0 Socket的CEM board:

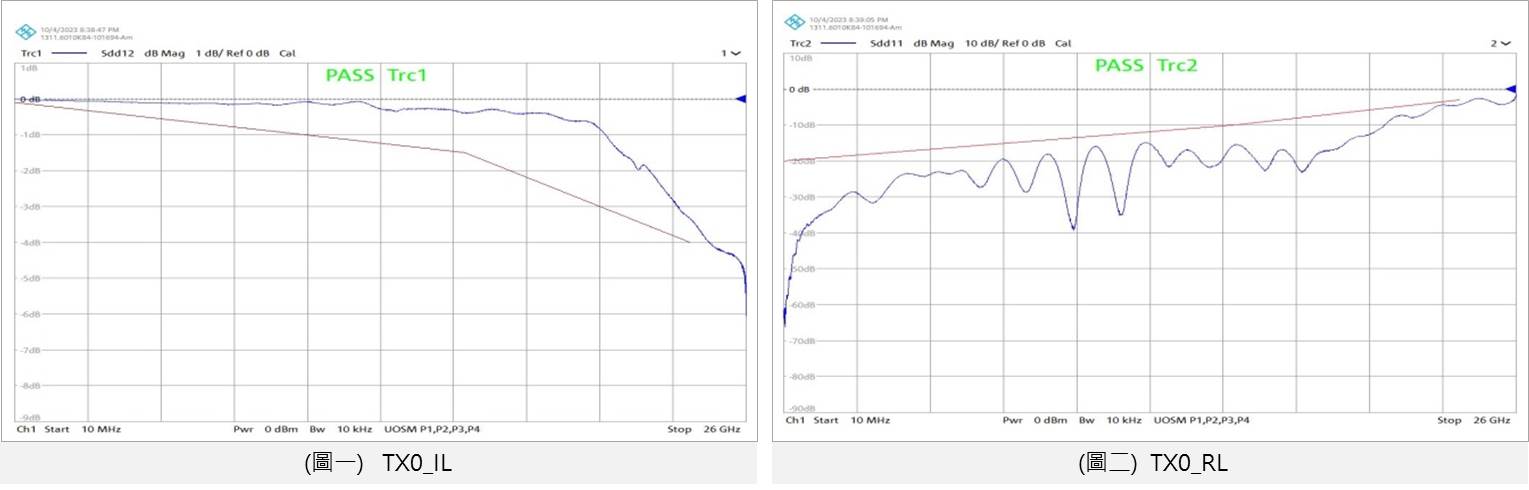

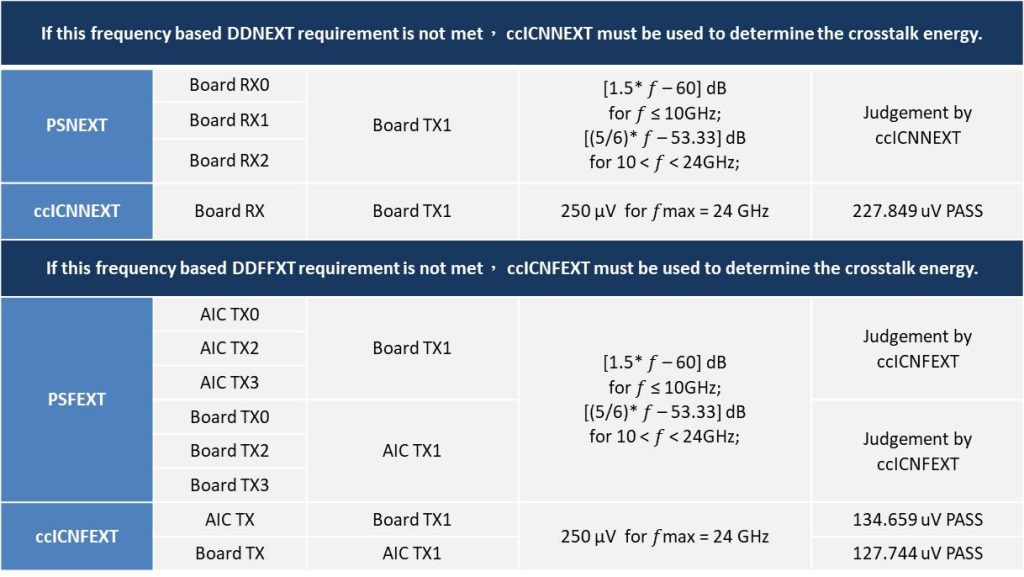

下图一、二为实际量测Allion PCIe 5.0 Socket CEM board TX0的IL/RL的实际数据,以及整体NEXT/ FEXT的结果(仅供参考):

*AIC: Intel PCIe Gen 5 Add-in Card

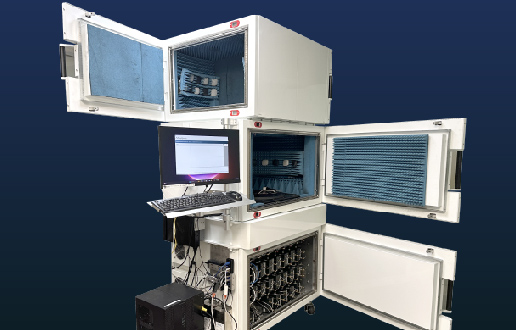

百佳泰同时拥有高阶的向量网络分析仪(Vector Network Analyzer),最高带宽高达67GHz,能够准确量测治具的高频特性,呈现真实且准确的设计结果。

百佳泰在标准治具或客制化的治具设计有着以下的优势:

Faster

百佳泰不仅拥有超过30年以上的专业实绩、专业的技术团队以及一应俱全的测试环境与先进的仪器设备,在完成治具设计后能提供快速且正确的量测结果。

Easier

能提供一站式的治具设计及产品量测服务,与客户一同为产品质量进行严格把关。

Better

百佳泰累积多年的丰富项目经验及能力,有充足的量测经验来解读仪器的曲线含义,并提供解决方案的建议,帮助客户解决问题以加速产品上市时间。

若您对于治具设计相关的顾问服务有进一步需求,欢迎与我们联系,百佳泰服务团队将诚挚为您服务!