高速传输大量数据的需求,带动着USB4、HDMI、Thunderbolt及DisplayPort等高频连接器相继问世。举例来说,HDMI 2.1在4个信道上传输速度可达12Gbps;最新USB4规格让传输速度最快可支持40Gbps,Thunderbolt™ 4 埠具有与 Thunderbolt™ 3同样的40Gbps带宽。当讯号速度持续加快时,如何降低噪声干扰成了重要课题。

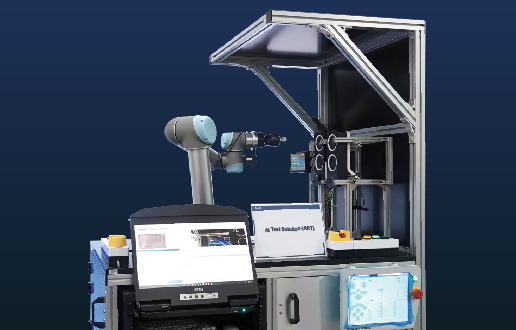

图1:HDMI、Thunderbolt及DisplayPort等高频连接器

现阶段,线缆连接器必须克服许多高频信号问题,包含:衰减(Attenuation)、反射损失(Return Loss)、耦合问题(Crosstalk)、阻抗(Impedance)、走线(Trace)以及走线长度。然而,多少频率以上称之为高频呢?400MHz、1GHz、5GHz还是10GHz呢?

如何避免反射波长

其实,高频的定义可以看成是否有反射发生:当电磁波在介质(空气或PCB)上传递的时候,如果是连续介质,则不会反射;撞到不连续介质时,若没有反射发生,则该频率在这个介质上视为低频;反之,若产生了反射,则视为高频。因此,我们常常会听到一种说法:「反射与波长有关」。

电磁波的传递速率又该如何跟波的运动结合呢?电磁波在空气或真空中的传递速率为光速

![]()

而电磁波在介质中传递的速率为

![]()

因此我们可以用此公式简单的算出电磁波在介质(例如:电路板)上的传递速率。

![]()

此时将波的速率与电磁波的速率公式合并,则可以获得电磁波在介质上传递时的波长:

波的反射概念:传递路径的长度小于传递波长的 ,在此条件下不会发生反射。

简单的来说,为了避免反射的发生,我们可以让在PCB上走的电磁波的波长越长越好( 大于Trace长度的4倍)。由以上公式可知,降低频率与降低PCB的相对介电系数,即可让波长变长。但实际上因为传输需求,数据的传输速率无法随心所欲地将频率降低,PCB的介质也不可能为1。

另一个方式:缩短Trace的长度,让其长度小于传递波长的 。或许这个是个可行的方法,但是当传输速率越快又或者高频组件之间的位置限制,高频Trace可能会有需要5~10cm的长度,缩短Trace长度又似乎未必可行。

高频走线与阻抗设计

提到电路板的高频走线,就会想到Trace的阻抗设计(Single-End 50Ω或者Differential 100Ω),而上面的说明却都没有提到任何的阻抗问题?上面所提的重点是:在无反射的条件下,不管频率多高,Trace就没有阻抗问题,亦即不需要做任何阻抗设计。

上一段提到,随传输速率越来越高,缩短Trace 长度几乎不可行。因此,拉长Trace必然会有反射产生,根据电磁波理论,不产生反射的另一个方法就是:Trace阻抗 = 负载阻抗 = 内阻抗。

既然是浅谈,就避开深奥的理论。以这个概念来看:Trace阻抗 = 负载阻抗 = 内阻抗,其实也是符合一开始所说的:只要是连续介质就不会有反射发生。也就是说,三者阻抗相同,就等于阻抗从头到尾是连续的介质。

反射与信号误判

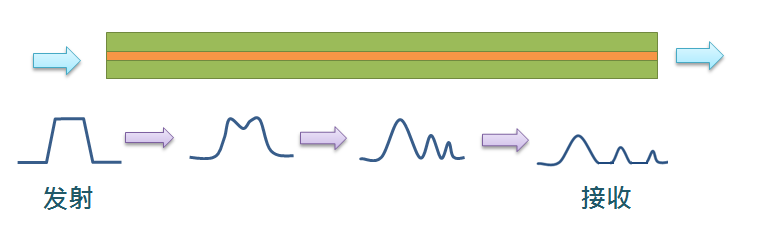

为什么不希望反射出现?反射意味着部分能量没有被传递出去而返回到原处(发射端)。这好像没什么,只要把发射端的能量再加大满足接收端所需即可。但实际上,返回的能量会从原处再反射一次,因为波有迭加的性质,二次反射到接收端的波会与另一个波迭加,因而产生信号不完整。以数字信号来看,在接收端原本是1的信号因此可能变成0,而原本是0的信号而变成了1,造成了信号的误判。

PCB板材挑选攻略

了解了反射所产生的信号问题后,还得挑对PCB,才能着手设计高频PCB板。较常看到的有两种PCB板材是FR4 与 Rogers。

PCB中的其中一项参数——相对介电系数左右了信号质量的优劣

![]()

相对介电系数与频率有关,频率的高低变化伴随着相对介电系数也跟着不同。这代表了甚么呢?由公式可以知道

以及

当相对介电系数随频率高低而改变的时候,走在PCB板上的电磁波传递速率跟着变化、波长也跟着变化,此即是电磁波理论所提出的色散(Dispersion)现象,这种介质称为色散介质或色散材料。色散对传输有甚么影响呢?

色散问题全面剖析

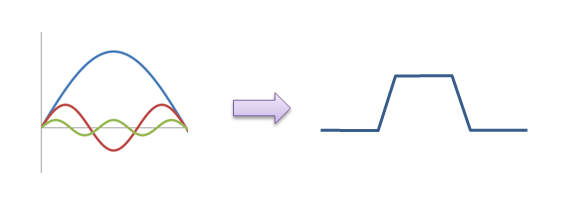

数字符信号是以方波的方式传递,也就是0跟1;从单一个的方波来看,他是由无数个不同频率的sin波形成。简化来看,由一个基本波与两个奇次谐波迭加而成:

图2:一个基本波与两个奇次谐波迭加成数字方波

当三种不同频率波在PCB Trace上传递的时候,此时由于相对介电系数跟着不同,因此传递速率也跟着不同。也就是理想上,三种频率速度相同,因此传出到接收端还是一个完整的方波信号,但实际上,则不然:三种频率有各有不同的速率,有的跑得快,有的跑得慢。如果Trace拉得够长,反而会让方波分解成三种频率的电磁波,并以不同的时间到达接收端:

图3:Trace与三种频率

相同的High的信号,却不同时间到达,振幅也下降,这会造成接收端判断错误造成误码。再者,这只是一个High的信号,如果后面又接连好几个High跟Low信号,而后面速度快的超越了前面速度慢的波,此时接收端就更无法判断数据的正确性。

上期说过,虽然我们设计了Trace阻抗(single-end 50Ω 或 differential 100Ω),可以让Trace走很长也不会有反射的发生,但是当遇到色散介质 ∈r ( f ),也就限制了Trace长度。因此,即便我们做了阻抗设计,仍还是希望Trace走线能够设计多短就多短。

FR4与Rogers材料比较

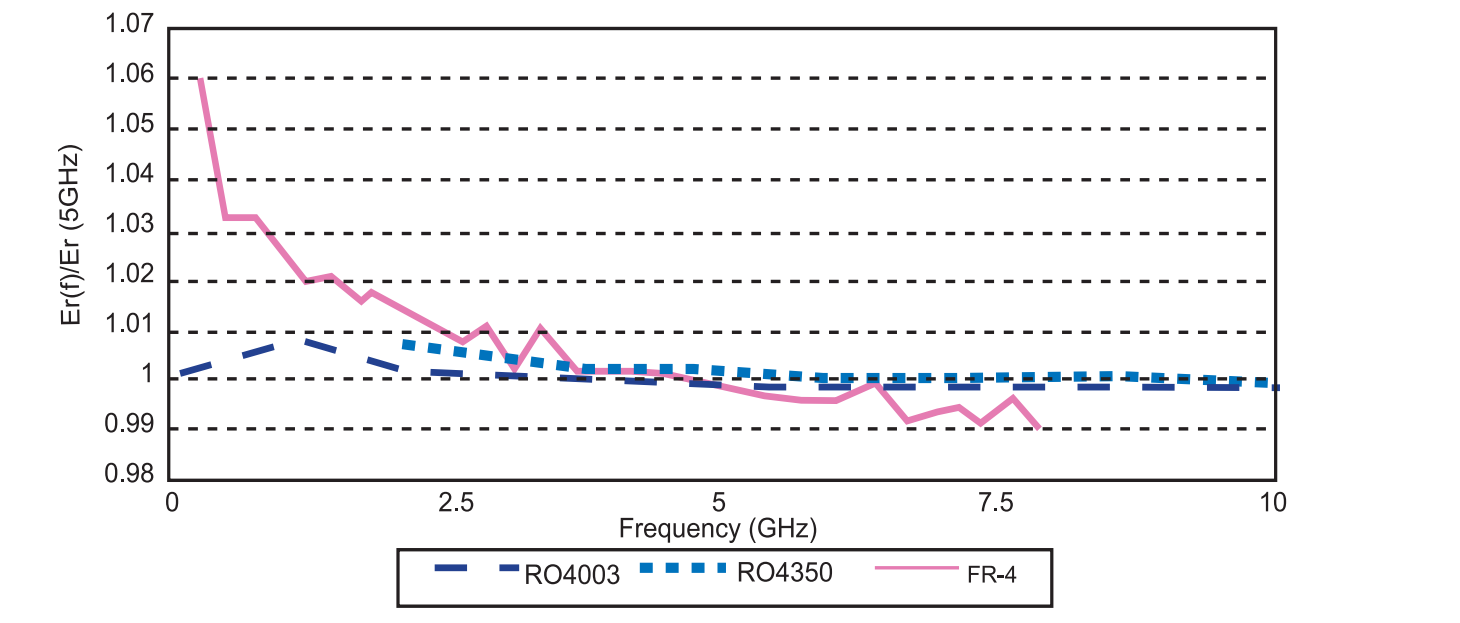

有了相对介电系数与色散现象的概念后,现在来看FR4与Rogers的材料。下图3是FR4与Rogers的相对介电系数对频率的变化:

图3:FR4与Rogers的相对介电系数对频率的变化

(数据源:RO4000® Series High Frequency Circuit Materials DATA SHEET)

由图3可知,FR4的 ∈r ( f ) 对频率变化相当剧烈,而Rogers(RO开头系列)则稳定许多。假设今天使用的传输速率的频率范围很宽,例如:PRBS31,那么选择FR4就必须相当注意色散问题,若要降低色散问题,Trace就要尽可能的短。

大家或许会说:为了一劳永逸,干脆直接选择Rogers板材,问题就解决了!这个答案是正确的,但是因为Rogers板材成本很高,所以必须三思。该怎么降低成本、信号质量又该如何维持而能达到通讯的需求?一直是专业的Layout工程师思考要如何取得平衡的点。

最后,为什么我们这边一直没有提到 ∈r ( f ) 对Trace阻抗的影响呢?实质上是会影响的,但是为了避免分析与说明太过于紊乱,因此把阻抗设计的问题理想化。

PCB板的Layout设计

上文说明了高频与电路板之间的关系,例如如何挑选合适材料又兼顾成本考虑。本篇要来和大家分享高频PCB板设计的最后一哩路,也就是PCB上面的Layout设计。

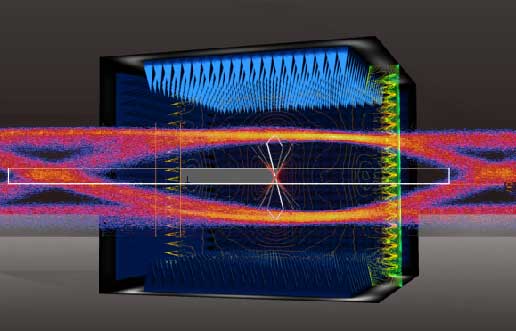

PCB上的Layout该怎么设计呢?大家第一个反应就是:跑模拟。模拟软件相当便利,可节省不必要的成本与时间,但是模拟参数该如何制订?预期的模拟结果该如何计算?首先须具备核心概念才能着手进行Layout设计,因此本篇短文会针对波导结构进行介绍。

3大波导结构优缺点分析

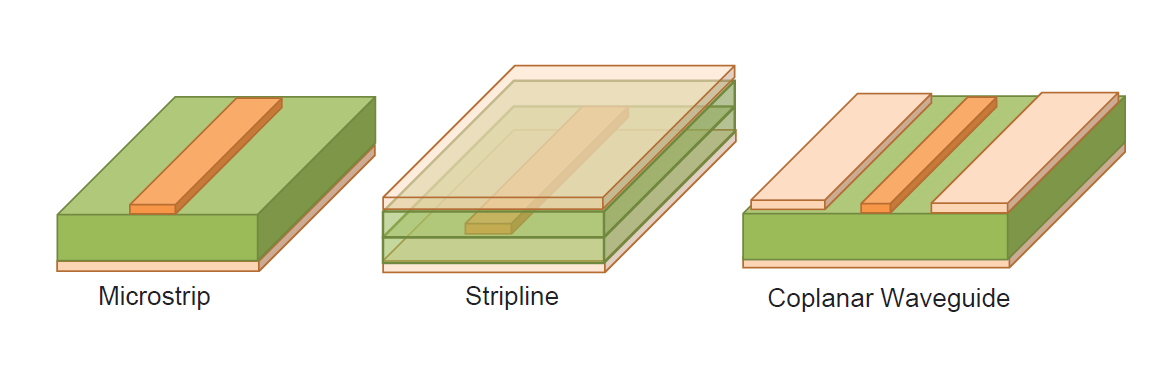

在制作高频电路板的时候,第一个问题就是波导结构的选择。本篇介绍三种基本的传输结构:Microstrip、Stripline以及Coplanar Waveguide(共面波导)。

图5:三大波导结构

Microstrip:架构最为简单,设计也简单。但由于架构简单,在相同的PCB基板条件下,能够变化的物理参数不多,例如线宽、线厚与基板厚度。

当频率越来越高,Microstrip还会有一个问题:Trace上方是空气 ∈eff = 1,而下方的基材 ∈eff ≠ 1,此上下场型会有不对称的情况发生,而使得电磁波场型不对称,在传输上对信号质量会有影响。

Stripline:结构较为复杂,上方与下方基材的 ∈eff 可以使用接近基板,使得电磁波的场型完整。另外,Stripline高频走线相互之间不会有远程串音(FEXT)的影响。

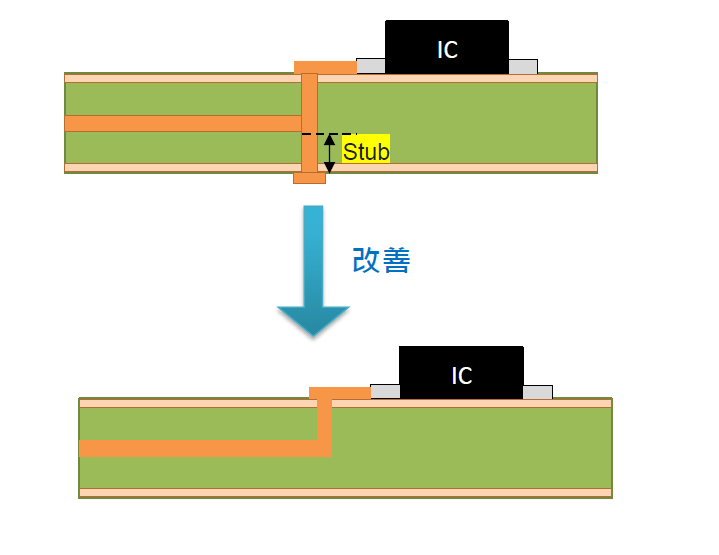

由于走内层,需要依靠灌孔与外部零件连接,因此多余via段(称为Stub)会造成信号衰减与反射问题。减少此问题的方法就是使用背钻或是盲孔,但这又会导致成本上升。

Coplanar Waveguide:类似Microstrip,走线的两旁用ground包覆(铺铜导地),形成Waveguide的形状。而相较于Microstrip,Coplanar Waveguide能够变化的物理参数就比较多,例如走线与ground的距离、ground上的via与走线距离。

由于Coplanar Waveguide两旁是GND,因此可以降低Crosstalk的影响。但在设计上有个瓶颈:当应用上有密度较高的高频走线的时候,例如PCIe,则此结构未必有足够的空间可以在走线的两侧铺铜接地。

本篇PCB技术浅谈,着重在波反射、信号误判、板材挑选、波导结构等,事实上高频PCB的设计与制造还须考虑众多量测参数,包含S参数、串音耦合、PRBS、DC Balance(8B10B)等等,后续有机会将会继续用技术短文的方式与大家分享。

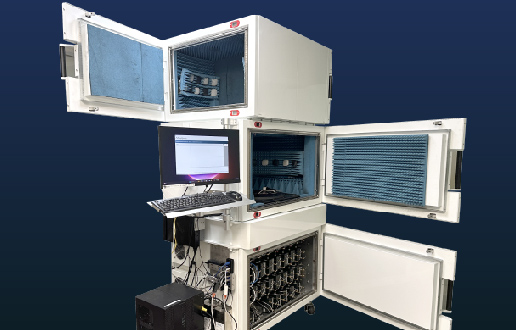

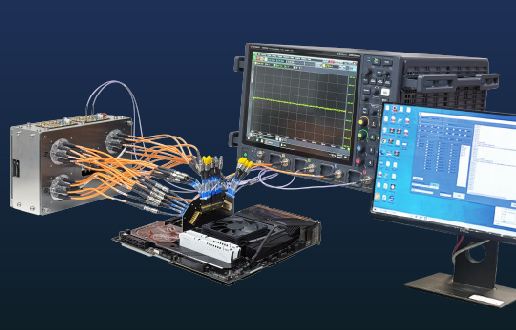

高频量测与治具设计服务

目前唯有百佳泰能提供客户从图样、产品Sample到治具,全方位从验证测试、设计改善、到取得证书,协助您大幅缩短产品开发时程,成为市场中有竞争力的高质量产品。若有关高频量测或测试治具需求,请洽百佳泰 service@allion.com 获得进一步信息。