实际案例说明

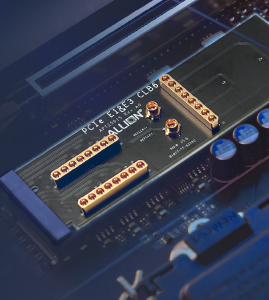

客户为高性能平台开发厂商,在新一代平台进行 DDR4 Electrical Validation 时,除既有的 DRAM Side 合规测量需求外,进一步希望同步掌握 CPU Side DDR 信号质量表现。通过双端点测量,从系统角度评估整体通道设计是否具备足够的设计裕量,作为后续参数调校与风险评估的重要依据。

客户需求与实务挑战:

由于该平台在设计初期未针对 DDR 高速信号预留 DRAM Side 测量点位,使得后续验证阶段无法直接依循 JEDEC 规范进行标准电气测量。因此,即使客户具备完整的测量设备与测试能力,仍因测量接口受限,难以取得具代表性且可用于合规判定的数据,成为验证流程中的首要瓶颈。

客户并非仅关注单一端点是否通过规范测试,而是希望从整体系统角度,全面掌握 DDR 内存通道的实际信号质量表现,包括:

- 同步比较 DRAM Side 与 CPU Side 在 DDR4 电气行为上的差异。

- 厘清是否因通道走线、封装效应或 SoC PHY 设计因素,导致 Timing Margin 被压缩。

- 转化测量观察为可行的系统设计回馈,支持后续的参数调校策略,如 Read/Write Leveling 与 ODT 设置优化。

- 實務執行上,CPU side量測受限於探棒接觸空間不足、波形擷取困難

- 量測結果與 JEDEC 規範之間不易直接對應,使內部團隊在驗證策略規劃與數據解讀上承受相當壓力。

百佳泰顾问团队以顾问式验证流程,协助客户整合 DRAM Side 与 CPU Side 的测量结果,将数据转化为可回馈至系统设计的实务判断。

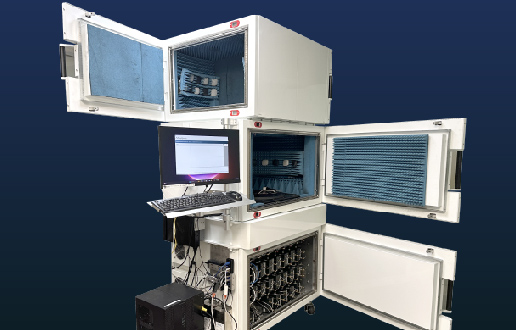

解决方案:规范导向 × 系统观点的整合验证策略

针对上述需求,百佳泰顾问服务团队导入“规范导向分析 × 系统层级解读”的验证流程,协助客户建立可落实的验证架构

-

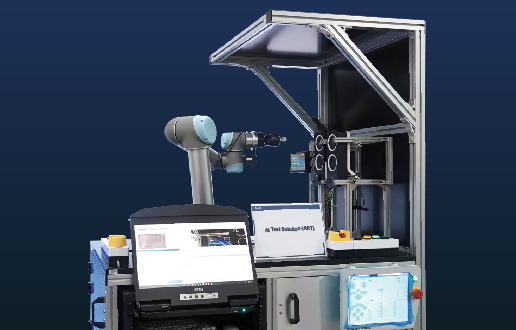

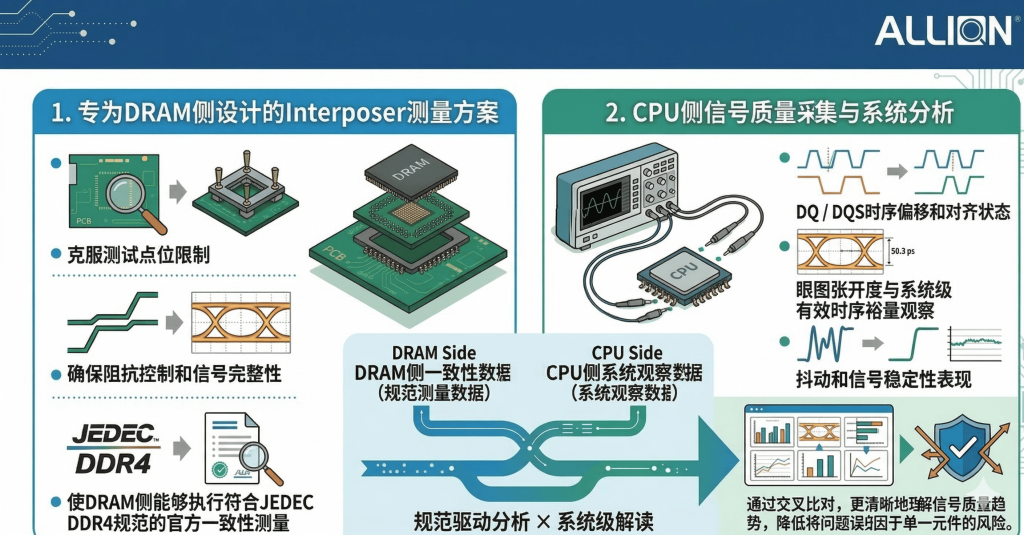

专为 DRAM Side 设计的 Interposer 测量方案

凭借多年高速治具设计与内存测量经验,百佳泰为客户量身设计 DRAM 测量治具(Interposer / Spacer Board):

- 补足平台缺乏测试点位的限制。

- 确保阻抗控制与信号完整性。

- 使 DRAM Side 可执行符合 JEDEC DDR4 规范的正式 Compliance 测量。

-

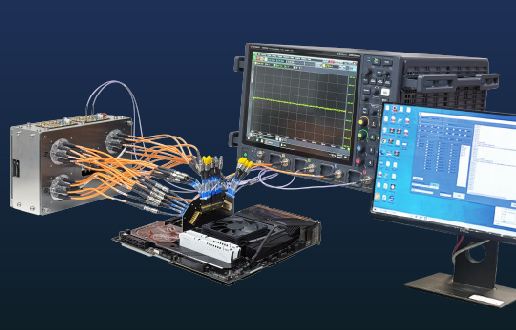

CPU Side 信号质量获取与系统性分析

在完成 DRAM Side 规范测量的同时,依客户需求在 CPU Side 获取对应的 DQ/DQS 波形,使用高带宽示波器与低负载差分探针进行分析,重点包含:

- DQ/DQS skew与对齐状况

- Eye opening与系统层级的有效 timing margin观察

- Jitter与讯号稳定度表现

CPU Side 测量并非用于 JEDEC 规范判定,而是作为系统内部相对比较与通道行为观察之用。通过与 DRAM Side 规范测量结果进行交叉比对,可更清楚理解信号质量在通道中的变化趋势,并降低将系统性问题过度归因为单一元件或工艺因素的风险。

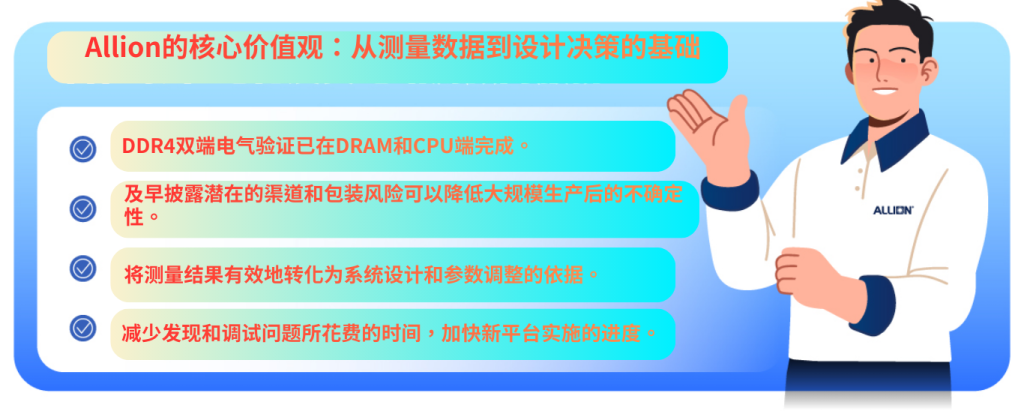

百佳泰的核心价值:从测量数据走向设计决策的关键依据

通过本次整合验证项目,百佳泰协助客户:

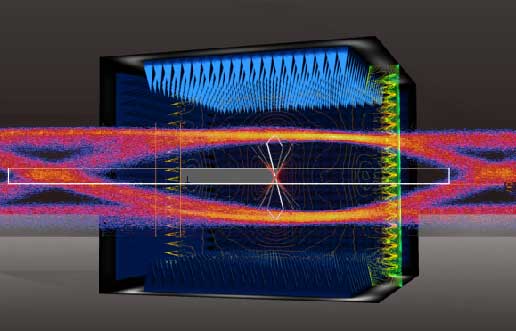

DDR 验证不仅是“合规”,而是“可用且稳定”

在高速内存设计中,真正的挑战不在于是否符合规范,而在于系统是否具备足够的设计裕量与长期稳定性。通过结合标准化测量、专用治具与系统层级分析,百佳泰协助客户从单点验证走向整体通道理解,让 DDR 电气验证成为可支撑设计决策的关键工具。

未来,百佳泰也将持续以专业测量能力与顾问式验证经验,成为高性能计算与服务器平台在高速内存设计领域中,值得信赖的长期技术伙伴。