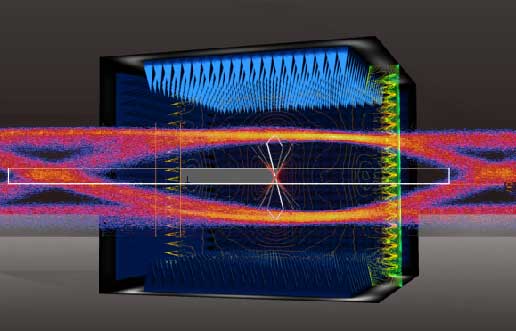

自从AI服务器、GPU加速卡、NVMe SSD、工业计算机、高阶主板与交换器平台快速演进,PCIe早已不只是接口名称,而是牵动整体系统效能、稳定性与兼容性的关键枢纽。不管是信道速率持续提升、板材与走线设计日益紧凑,或是异质整合与Retimer/Redriver组件导入成为常态,这些变化正全面翻转PCIe电气特性验证的角色定位。百佳泰以关键工程化流程 ,将高速接口导入的挑战化解,将量测结果成为可交付、可沟通的工程证据!

PCIe应用困局与导入风险有哪些?

多数客户在项目中最核心的需求

不是测不到!而是「难以确定测得对」

在PCIe这类高速差分接口上,真正的痛点时常不是「是否执行过测试」,而是以下的实务难题:

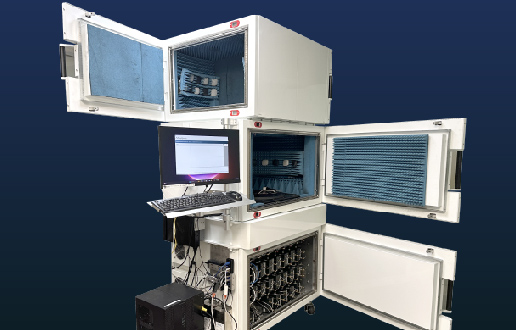

- 内部资源与设备门槛高

高速电气量测牵涉高频示波器、探头/探棒、治具设计、校正流程与工程经验,前期投资与长期维护成本高。 - 量测结果难以重现与比较

不同治具、校正方式与测试条件,往往造成「数据看似接近,但结论差异大」,导致内部难以形成一致判断。 - 跨团队沟通成本高

硬件、SI/PI、韧体与系统整合团队各自解读数据,若缺乏一套可追溯的测试计划与报告架构,问题往往难以快速收敛。 - 终端客户与品牌商要求日趋严格

客户不再只接受pass/fail结果,而是要求清楚的量测条件、测点定义、裕量分析与第三方验证背书。

这意味着许多项目常常卡在「产品已接近完成,但验证证据不足」的关卡,后续不是被迫延迟出货,就是带着不确定性进入量产,导致可能后续再以更高成本补救。

应用工程化流程 交付PCIe电气特性测试与可用结论

如果你还在觉得百佳泰的PCIe电气特性测试的价值仅在单次量测,那你就错了。来看看百佳泰如何协物将测试转化为可交付、可追溯、可沟通的具体工程成果:

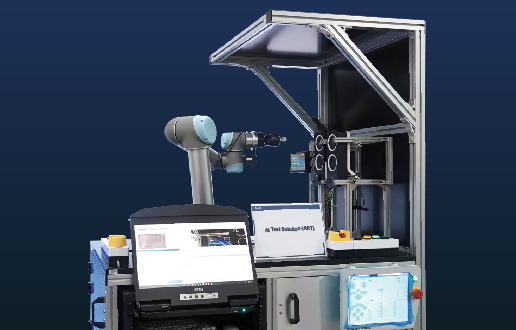

测试规划

依产品形态(Add-in Card、主板、背板、Cable、Retimer/Redriver)与客户验收需求,定义测项、测点、测试条件、样品与批次策略,并建立风险优先序。

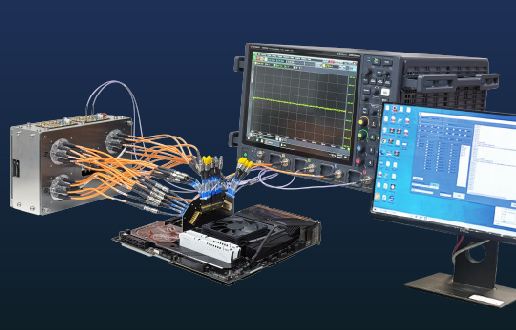

第三方测试报告

以第三方立场提供完整报告,涵盖量测设定、校正方法、波形结果、裕量分析与判读依据,作为对外验证与稽核依据。

量测治具与校正机制

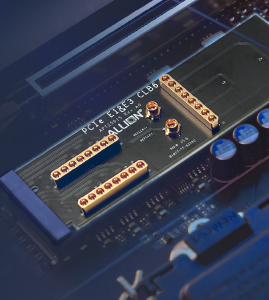

- 在PCI-SIG仅针对标准CEM形态定义官方量测治具的情况下,百佳泰已依实际产品应用需求,自行开发并累积多种非CEM形态之量测治具,涵盖OCP NIC、EDSFF E1 与 E3、2、U.2等常见高速接口与储存模块形态,并且可针对实际走线、连接器与系统结构协助客制化治具。

- 治具设计皆纳入完整的校正流程与误差控制机制,以提升量测结果在不同产品形态与平台间的可重现性与可比较性,并可支持最新PCIe 6.0规格,适用于多元高速产品应用情境。

问题现象分析与除错支持

除提供量测数据与测试结果说明外,亦协助问题现象的初步分析,并依量测观察结果提出可能的设计、布局、材料或参数调整方向,供客户于后续设计与验证阶段参考,以协助测试结果与实际设计决策之衔接。

从「不确定」到「可交付」,将验证成本转化为显著竞争力

补足内部测试资源不足

无需为少量但高门槛的高速量测投入长期设备与人力,让内部工程师专注于架构设计与问题修正。

满足终端客户对验证证据的期待

透过可稽核、可追溯、格式完整的测试报告,缩短品牌商与系统厂审查时间,降低反复补件造成的项目延迟。

建立对外沟通的信任资产

第三方报告提供公信力背书,工程批注提供可落地的改善路径,在客户验收、跨国供应链协作或客诉厘清时,成为最有效的共同语言。

给正在打造高速平台的你:与其赌「应该没问题」,不如用数据提前把关

PCIe的问题往往不是「完全不能用」,最可怕的是只在特定负载、温度或平台条件下才会浮现。因此,越早以正确的方法收敛不确定性,越能将成本控制在研发阶段。

若你正面临验证时程紧迫、内部设备与人力不足、客户要求第三方测试报告,或需要治具与测试计划支持,百佳泰可依你的产品形态与交付目标,提供对应的PCIe电气特性测试方案与报告交付,协助你把高速设计化背后的风险,确实留在实验室。

有烦恼,就来问!百佳泰专家为你解答

无论产品、行业还是生态圈,填写表单就能问专家!